# 石英晶體的特性

## 壓電效應對石英晶體的影響

石英晶體片有一個特質當壓力應用於晶體軸的方向、電會更改在石英晶體片上或相反,電力應用於石英晶體片,晶體片內會有失真。因此,這就是爲什麼我們叫它是壓電石英晶體的影響。

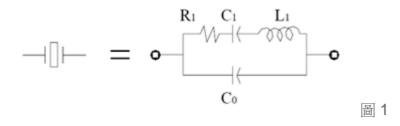

#### 晶體的等效電路

石英晶體的等效電路顯示解釋關於晶體特徵和性能的基本元素。 它包括的元素有動態電容  $C_1$ 、電感  $C_1$ 、系列電阻  $C_1$ 、和分支的電容  $C_2$ 。 前三個參數被稱爲石英晶體元素的動態參數。 請參見圖 1

## 串聯諧振 (Fs)

當晶體在串聯共振 (Fs) 下運行時,它看起來在電路中電阻。 因此,在共振阻抗是幾乎為零。 在一個好的設計系列諧振回路,相關性不是一個問題和負載電容不必指定。 請參見圖 2

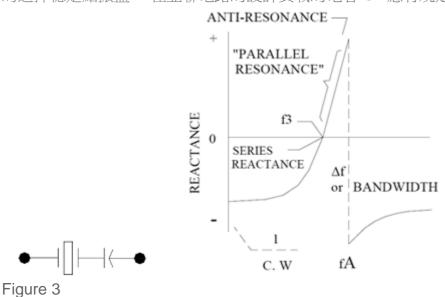

## 並聯諧振

當晶體並聯共振下運行時(Fs < Fl < Fa),它看起來電感在電路中。因此,負載電容的作用是非常重要的選擇穩定點振盪。在並聯電路的設計負載的電容 CL 應有規定。請參見圖 3

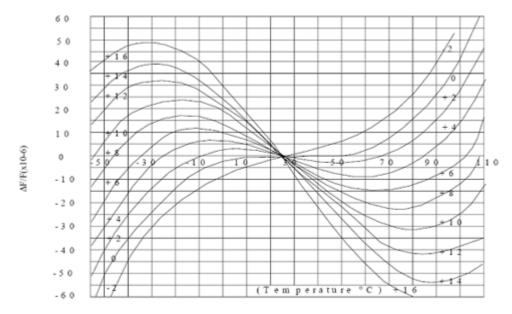

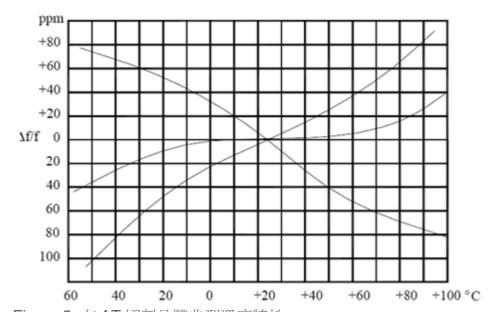

## AT 切割和 BT 切割晶體之間的差異

AT 切割的晶體和 BT 切割的晶體是擁有不同的切割角度 (AT 切是 35 度與 BT 切是 49 度)。 這兩個類型具有相同的振動模式(厚薄切變)。 但是,用 BT 切割 50 兆赫的晶體片是稍厚(2mils)相比其 AT 切

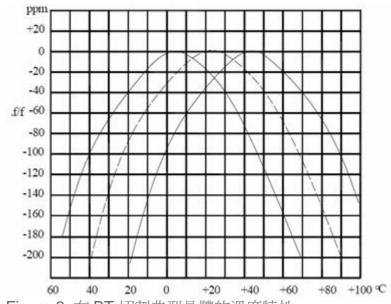

Figure 4. AT 切頻率溫度曲線

Figure 5. 在 AT 切割晶體典型溫度特性

Figure 6. 在BT 切割典型晶體的溫度特性

## AT 厚度減少與 BT 切割晶體

AT Fundamental

$$F = \frac{1670}{t}$$

AT Overtone  $F = \frac{1670 \times n}{t}$

$$\begin{cases} F \text{ in KHz} \\ t \text{ in mm} \\ n \text{ = overtone mode} \end{cases}$$

BT Fundamental  $F = \frac{2560}{t}$

# 晶體單元的定義

## 品體單元

有一個外殼包的石英晶體 (二氧化矽) 或晶體帶真空镀金屬電極和終端連接的情況。它廣泛用於電子的被動元件爲行動電話、無線設備、電信設備、個人電腦和其他數位設備。

## 頻率

每秒有多少個波形的週期輸出。 該單位的頻率為每秒週期,或稱赫茲,簡稱赫。

## 基諧振動模式

晶體的主要模式。 它也被稱為第一泛音。

#### 泛音振動模式

奇數在指定的頻率振盪模式的指定條款。第三泛音模式標準,其次是第五,第七,第九,等頻率不完 全三,五,七,或基頻的九倍。

## 頻率公差

這是指允許頻率偏差數以百萬計的百萬分率(ppm)通常在室溫 + 25C°。

#### 頻率穩定度

這指的是允許的最大頻率偏差在指定的溫度範圍內(+25C°)相比的測量頻率,如 -10~+70 C°。

#### 等效串聯電阻

阻抗的值在操作時會出現在晶體諧振電路。

#### 並聯電容

並聯電容(CO)是在晶體之間的電容端子。它附在包裝內,表面貼封裝通常是比較小(4pF 典型值),插腳的封裝約 6pF。

#### 負載電容

這指的是在的晶體外部電容和電容量量度或通過 PCB 上的晶體終端。晶體在並行模式下負載電容是需要指定使用的。 如果應用程式需要的"串聯"共振頻率晶體,負載電容,並不是一個因素,並不需要指定。 負載電容的計算公式如下:

$$CL = \frac{(C_1 \times C_2)}{(C_1 + C_2)} + Cstray$$

## 絕緣電阻

晶體腳部之間的電阻,或腳部及鉛外件 (金屬外殼) 之間。 它測試在直流電壓 100V ±15V 的和絕緣電阻 是 500 M  $\Omega$  (最少)。

#### 驅動電平

在振盪電路中晶體所經歷的功率消耗的量。電力應用功能是通常表示在毫瓦的。 過多的驅動電平將導致可能長期頻率漂移和不穩定的操作增加老化率或晶體骨折。 驅動電平可按以下公式計算:

Power =  $(I \text{ rms}^2 * RL)$

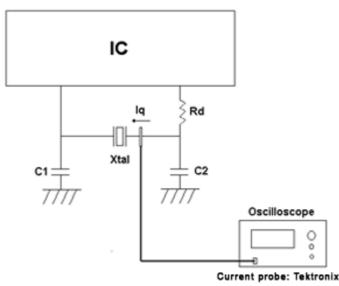

其中是通過晶體單元的有效值,R 是特定晶體單元的最大阻力值。這個電平方程式是指"歐姆法"。通過暫時在系列中與晶體設備插入一個電阻的振盪電路可能是實際的驅動電平測量。電阻必須的歐姆值爲單位。然後可以讀取整個電阻電壓降和當前和電源消耗計算。然後,必須刪除該電阻,作爲測量驅動電平的替代,可能在晶體空間許可的輸出腳使用當前的電平。該方法爲下

$$RL = R1 \left( 1 + \frac{C0}{CL} \right)^2$$

注:

RL = 載入的共振電阻

R1 = 共振性晶體單位

Iq = 當前流向晶體單位

C0 = 分流電容

CL = 負載電容

圖 7. 驅動電平測量

#### 老化

這指的是累積變化的頻率在一段時間。 在第一次的 45 天過程中,這樣率是變化的頻率的操作的快的。 許多關聯因素在衰老過程中所涉及的一些最常見的因素是:

- (1) 渦量的驅動電平,

- (2) 內部污染,

- (3) 晶體表面的變化,

- (4) 電線疲勞,

- (5) 各種熱效應,

- (6) 摩擦磨捐. 等等...

所有這些問題都可以通過適當的電路設計納入低工作溫度、最小驅動器級別和靜態最小預先老化。

## 衍生频率

它也是可能的振動頻率,其基本或泛音的頻率無關的晶體。 這種有害的頻率被指爲假。衍生频率通常是以上分貝最大中指定的操作模式。 或電子自旋共振的次數, 必須指定頻率範圍。

#### 工作溫度範圍

溫度範圍內的晶體指定的條件。

#### 振動模式

它是壓電石英晶體的效果。 石英晶體厚薄规在 AT 切割和 BT 切割的振動模式而有異的,如厚度剪切的晶體削減或長寬彎曲的音叉晶體 (+ 2°) X 切割。 最受歡迎的切割是 AT 切割,提供一個對稱頻移過寬的溫度變化。

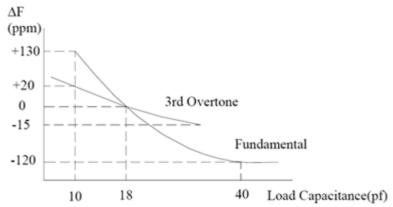

## 負載電容和牽引度的變化

晶體的牽引度(Pullability) 是指在並行模式下運行的水晶和頻率變化的一項措施是作爲函數的負載電容。牽引度是重要到電路設計器如欲實現一個單晶的幾個工作頻率變化的負載電容值的方式。 晶體並行共振的運行時(Fs < Fl < Fa),它看起來電感在電路中。 隨著該電抗的變化頻率更改相應,從而改變晶體的牽引度。 Fs 與 Fa 的頻率差異取決於晶體單元的 Co/C1 比例。 方程的兩個負載電容之間的牽引範圍如下:

$$D_{L1/L2} = \frac{f_{L1} - f_{L2}}{f} = \frac{C1(C_{L2} - C_{L1})}{2(C0 + C_{L1})(C0 + C_{L2})}$$

在第三泛音模式下的頻率相同晶體會有更少牽引,因爲其振動電容  $C_1$  是大約 1/9 的基諧振動模式的  $C_1$ 。

頻率及第三的泛音晶體與基本的牽引度。 石英晶體振盪大眾對應于振動電感  $L_1$ ,而振動本身的彈性由振動電容  $C_1$ 確定。

#### 晶體應用說明

本應用指述了用於任何類型的微控制器,接受一種並行模式晶體的選擇、 AT 或 BT 切割水晶、基諧振動模式或泛音振動模式。

#### 雷路描述

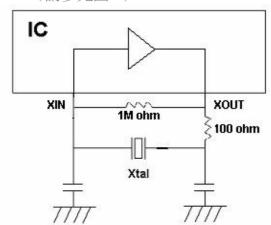

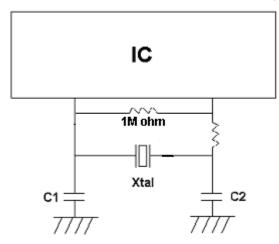

大多數晶片主動的回饋電阻 (典型  $1M\Omega$  )的一種逆變器設計包括一個可選系列電阻値更改從 100 到 1  $K\Omega$  (請參見圖 8 )。

#### 圖 8. 振盪電路

有一個通常稱爲 (XIN) 的輸入的埠和 (XOUT) 輸出埠的晶體連接之間的兩個埠。 大多數晶片的設計 與一個選項,或由一個外部晶體振盪器送入晶體的輸入埠或一個外部晶體。

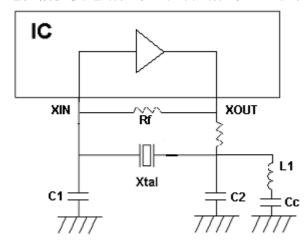

取決於頻率,晶體可以被選爲基本或泛音模式。通常,40MHz以上頻率的價格優勢和交付要求第三泛音模式。晶體電抗感應的並行模式在 C1 和 C2 兩個外部電容器所需的必要的相位的振盪。 C1 和 C2,晶體是否在基本模式或泛音模式。 C1 和 C2 的值通過指定的晶片製造商在 6pF 至 47pF 而有所不同。 C1 和 C2 可能不平衡, eg, 平等的價值,但有時爲了獲得最佳的性能取決於晶體和放大器的特性和主機板佈局的特定比例(C1/C2)偏移量。顯示基本模式操作的典型配置(請參見圖 9)。

圖 9. 振盪電路的基本模式

以泛音的方式同時抑制或拒絕基本模式選擇第三個泛音模式需要一個附加電感器 Ll 和電容 Cc。 選擇 Ll 和電容元件值在第三的泛音晶體電路以滿足下列條件:

- 1. 從一系列諧振電路,使電路的基本頻率低於頻率電感器和電容元件看感應基本頻率。 在基本模式下的振盪不贊成這種情況。

- 2. 電感器和電容 Cc 和 C2 元件形成一個平行的諧振回路中途基本和第三次泛音頻率之間的頻率。 這種情況使電路在第三泛音的頻率,主張在所需的泛音模式振盪電容。 (見圖 10)。

圖 10. 第三泛音頻率模式振盪電路

- 3. 在一個標準泛音模式下 C2 的値不同于 8pF 到 30pF。 應選擇 Cc 的値最少 爲 10 次 的 C2 值, 所以其等效的 C1 量 將大約 C2 的値。

- 4. 不同晶體頻率的 LI 典型值:

- 25 MHz 4.7uH, 6.8uH, 8.2uH, I0uH

- 32 MHz 2.7uH, 3.9uH, 4.7uH, 5.6uH

- 40 MHz 1.5uH, 1.8uH, 2.2uH, 2.7uH, 3.3uH

## 負阻

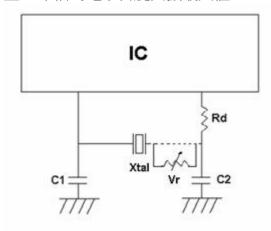

優化的性能的建議措施的振盪電路的負電阻。 如圖 11 顯示以下、 提高振盪電路從晶體的一端和插入一個可變電阻器較低的値開頭的。 監視與該的示波器的波形和示波器繼續增加插入 Vr (變電阻,) 的值,直到電路將顯示無振動信號。 值的振盪停止表示負電阻。 建議的振盪電路的負電阻值一般應至少五~十倍的電子自旋共振最大值。

圖 11 負電阻測量